# Addressing Delamination through Advanced Semiconductor Die Design

Rennier S. Rodriguez<sup>1\*</sup> and Frederick Ray I. Gomez<sup>1</sup>

<sup>1</sup>New Product Development & Introduction, STMicroelectronics, Inc., Calamba City, Laguna, Philippines 4027

### ABSTRACT

12 13

1

2

3

4

5 6 7

8

9 10 11

Innovations and breakthroughs are continuously driven in semiconductor manufacturing to overcome existing assembly limitations and recurring difficulties. This paper is focused on the resolution of the delamination issue during die attach assembly process. A new design of semiconductor die is presented to establish a robust adhesion or interface bonding between the silicon die and the epoxy material for die attach. The paper also provides the specialized design of manufacturing flow for the improved die design through advanced wafer fabrication method and wafer cutting technique. The realization of the advanced silicon die attach assembly process.

14

15 16 Keywords: Delamination; die attach process; leadframe; silicon die; wafer.

### 17 **1. INTRODUCTION**

18

19 The application of sintering glue or epoxy in silicon die attach process of quad-flat no-leads 20 (QFN) packages requires metallic layer in the backside of the die to enable intermetallic 21 connection between silicon die and sintering glue. Gold (Au) plated on the silicon backside is the common practice in terms of backside coating. Organic or non-metal does not create 22 23 sintering with the glue, thus it will only cause delamination between interfaces. In addition, 24 the presence of organic compound in leadframe such as anti-epoxy bleed-out or silicon 25 material produces "hydrophobic effect" to the glue which restricts the even wetting of the 26 glue to the surfaces. Studies on delamination and anti-epoxy bleed-out are shared in [1-5]. Die attach delamination in QFN packages is the separation of die attach material to silicon 27 28 die and leadframe pad. Important to note that with the continous technology trends and 29 breakthroughs, challenges in assembly manufacturing are inherent [6-8].

30

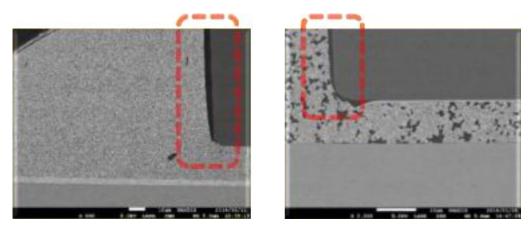

A scanning electron microscope (SEM) image photo in Fig. 1 shows the cross-sectional view of a die that is attached to a sintering glue. The backside which is Au-plated holds good intermetallic connection with the glue while delamination is observed on the junction (bare silicon/non-metal) part of the die. When aggravated, small delamination may propagate and worsen which can cause a complete delamination of the silicon die to the glue or the delamination may also propagate to the other interfaces inside the QFN packages such as mold-silicon die or mold-leadframe interfaces.

\*Corresponding author: Email:

#### 41 42

### Fig. 1. Cross-sectional view of silicon die interface with glue

The paper is focused on the improvement of the silicon die design that would eliminate the occurrence of delamination on non-metal area such as side junction or sidewall of the die. To fabricate the proposed design, a half-cut is performed on the backside of the silicon wafer then metal such as Au or Silver (Ag) is deposited on the bottom surface. A full cutting will be performed afterwards to separate each individual die. In this design, the sidewall will be incorporated with Au or Ag metal that will enable intermetallic connection of the glue.

49 50

51

## 2. DESIGN SOLUTION AND METHOD

The formation of epoxy fillet height on the sidewall of the die is a normal behavior of the glue when a die is attached. the surface resistivity of the leadframe, during wetting of the glue, restrict the continuous flow of the glue along the pad thus excess glue will be redistributed to the sidewall of the die wherein there is less surface resistivity. On the other hand, an interface of sintering glue and silicon die, during sintering glue process, will occur on the package.

58

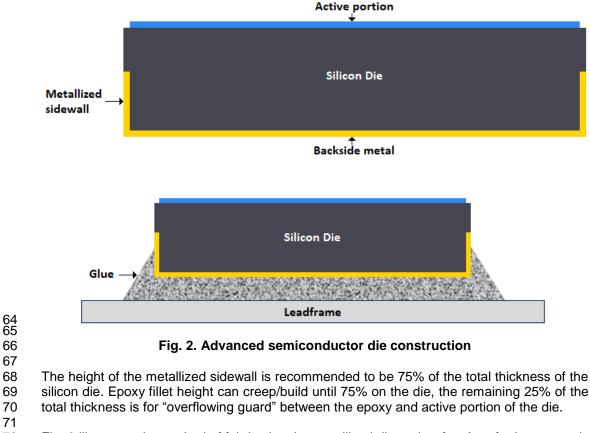

A silicon die with metallized sidewall design introduced in Fig. 2 is a potential solution to eliminate the delamination formed between the interface of sintering glue and silicon, which occurs on the sidewall. The excess glue building on the sidewall will form intermetallic bond on the metallized sidewall.

63

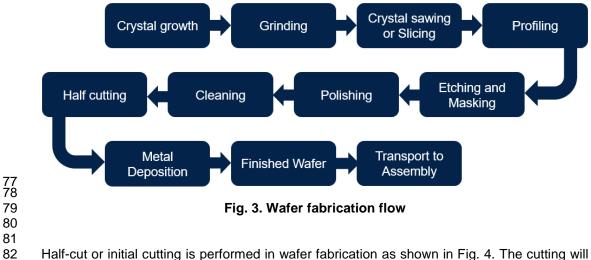

72 Fig. 3 illustrates the method of fabricating the metallized die and wafer. A wafer is commonly 73 made-up of silicon material that will be formed into individual slice through series of crystal growth, grinding, sawing and profiling. The active element or microchip on the wafer is 74 75 formed through different etching and masking technique.

76

- 80

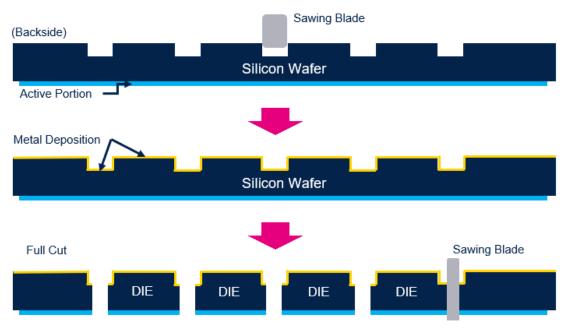

- 82 be performed at the backside of the wafer which can be done through infrared technology. 83

- 84 The size of the blade used to perform the first cut is dependent on the sawing street width.

<sup>\*</sup>Corresponding author: Email:

The blade width can have 60-70% of the total saw street. In example: a 70 µm blade width

86 can be used for 100 μm saw street. Afterwards, the metal will be deposited on the backside

and half-etch area. Technique can be through plating or immersion process.

Fig. 4. Wafer cutting technique

93 To completely isolate each individual die, a full cut is required. This process is performed 94 from the start of the manufacturing process. A blade is required to have a width of 40-50% of 95 the sawing street. A smaller blade is necessary to avoid damaging the metal sidewall of the 96 die during the final cutting or full cutting.

#### 97

89 90

91 92

### 98 3. CONCLUSION

99

The paper presented a new semiconductor die design with metallized sidewall for establishing a robust interface with the epoxy die attach material. With the improved design, die attach delamination issues could eventually be mitigated. Future works could adapt the new semiconductor die design to realize a robust die attach process and prevent any die attach related assembly issues. Finally, studies and learnings shared in [9-12] would help reinforce the robustness and optimization of die attach assembly process.

### 107 ACKNOWLEDGMENT

108

The authors would like to express sincerest gratitude to the Management Team and the NewProduct Development & Introduction (NPD-I) team for the continuous support.

111

### 112 **REFERENCES**

113

Buenviaje Jr. S, et al. Process optimization study on leadframe surface enhancements for delamination mitigation. IEEE 22nd Electronics Packaging Technology Conference (EPTC). Singapore. 2020;95-100.

- Chang M and Li A. Low stress die attach material challenges for critical Si node with Cu wire. IEEE 16th Electronics Packaging Technology Conference (EPTC). 2014;80-83.

- Neff B, et al. No bleed die attach adhesives. IEEE International Symposium on Advanced Packaging Materials: Processes, Properties and Interfaces. USA. 2005;1-3.

- Hsiung JC, et al. A surface energy approach for analyzing die attach adhesive resin bleed. Journal of Adhesion Science and Technology. 2003;17(1);1-13.

- Manikam VR and Cheong KY. Die attach materials for high temperature applications: a review. IEEE Transactions on Components, Packaging and Manufacturing Technology. 2011;1(4);457-478.

- Liu Y, et al. Trends of power electronic packaging and modeling. 10th Electronics

Packaging Technology Conference, Singapore; December 2008.

- Saha S. Emerging business trends in the semiconductor industry. Proceedings of PICMET '13: Technology Management in the IT-Driven Services (PICMET). USA. 2013;2744-2748.

- Yeap LL. Meeting the assembly challenges in new semiconductor packaging trend. 34th

IEEE/CPMT International Electronic Manufacturing Technology Symposium (IEMT).

Malaysia. 2010;1-5.

- Xian TS and Nanthakumar P. Dicing die attach challenges at multi die stack packages.

2012 35th IEEE/CPMT International Electronics Manufacturing Technology Conference (IEMT). Malaysia. 2012;1-5.

- 137 10. Graycochea Jr. E, et al. Process enhancement to eliminate adhesive film remains during

138 die picking. Journal of Engineering Research and Reports. 2020;11(3); 1-4.

- 139 11. Kahler J, et al. Pick-and-place silver sintering die attach of small-area chips. IEEE

140 Transactions on Components, Packaging and Manufacturing Technology. 2012;2(2).

- 12. Bacquian BC, et al. A study of die shear test performance on different diebond machine

platforms. Journal of Engineering Research and Reports. 2020;16(3);19-23.