# Die Attach Process Defect Mitigation through Design Improvement on Anvil Block Tooling

### ABSTRACT

Process improvement through modification in the design of indirect material is one potential direction to improve the productivity during assembly manufacturing. In this paper, an augmented design of anvil block is presented to reduce the crumpled strips, leadframe bending and dents, uneven bonding of die, localized insufficient epoxy, and misaligned die encountered during the conversion and setup stage. The implementation of the augmented design improves the current assembly practice through eliminating the replacement of anvil block that is the cause of misalignment on the indexer handler of the die attach machine. Through this design, the selection of appropriate vacuum hole setup can be through the sliding insert only without pulling out the anvil block from the machine.

Keywords: Anvil block; assembly; die attach process; leadframe; substrate.

### 1. INTRODUCTION

The application of machine for integrated circuit manufacturing reduced the risk of human intervention while increasing the efficiency of production and in-process controls. Latest die attach machine nowadays has a 50% placement capability improvement from the previous version of equipment with additional capability to automatically inspect and monitor the quality of all the units. Moreover, this translate to a 50-100% improvement, depending of the size of the package undergoing build, for unit per hour output with increased of production yield greater than 99.5%.

However, to attain the optimum performance of the equipment, a setup or machine conversion must be performed properly. The pre-requisite to produce a "machine recipe" for a certain package setup are: 1) programming of wafers and leadframe or substrate which requirement actual dimension, thickness, and position of the references and unit; 2) actual teaching of sensor and pattern recognition based from the leadframe and wafer programs; and 3) indirect material (or IDM) which pertains to the pickup tool, ejector needle assembly and anvil block toolings. Note that with new and continuous technology trends and breakthroughs, challenges in assembly manufacturing exist [1-4].

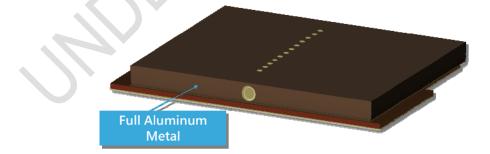

During IDM setup, in this case anvil block as shown in Fig. 1, human intervention and judgement is required to complete the job. Technician needs to perform the installation of the IDM to the machine based from the package or device requirement. IDM such as anvil block is dedicated according to the dimension and pitching of the leadframe as required by the package (i.e.  $5x5 \text{ mm}^2$ ,  $5x7 \text{ mm}^2$ ,  $6x6 \text{ mm}^2$ ). Upon installation, a manual calibration and planarity are required on the leadframe handler of the machine. The height of the bondhead assembly for every unit in a single row is required to be taught in the machine.

Fig. 1. Actual anvil block

Human interventions in the part of setup procedure are the causes of common assembly defects such as crumpled strips, leadframe bending and dents, uneven bonding of die, localized insufficient epoxy, and misaligned die. Opportunity is seen through modification of the anvil block tooling to provide a design that limits the replacement of anvil block thus reduced the cycle time of setup and conversion as well. This paper discussed the design of a flexible anvil block that can cater multiple packages. the design has a sliding process plate equipped with multiple vacuum holes that can be change depending on the requirement of the package. Through application of the design, anvil block is not required to be removed on the machine which secures the planarity between the indexer handler and positively impact the cycle time of setup and conversion on the machine.

## 2. PROCESS DESIGN AND METHODOLOGY

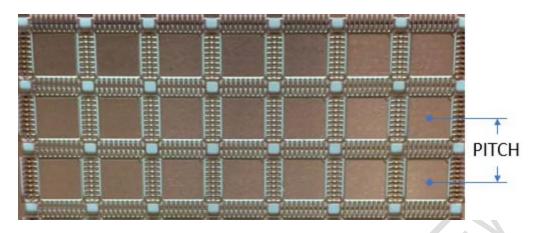

Die attach machine requires anvil block during dispensing and bonding to hold properly the leadframe during the process. Anvil blocks are made from metal plates drilled with a defined array of vacuum hole that is connected to the vacuum supply as illustrated in Fig. 2. The array of vacuum hole is equivalent to the leadframe pitch or the distance of every device or unit in a leadframe strip as shown in Fig. 3. In production practices, changing the leadframe design or pitch requires a dedicated anvil block design.

Fig. 2. Three-dimensional model of anvil block

Fig. 3. Unit pitch in a leadframe strip

### 3. RESULTS AND DISCUSSION

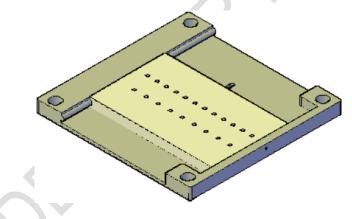

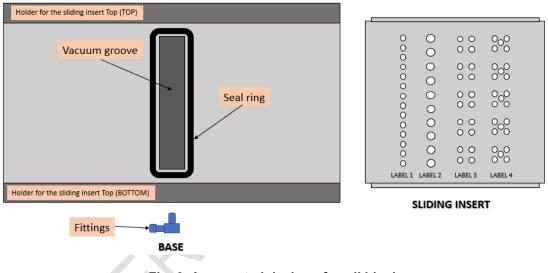

The augmented design of anvil block as shown in Fig. 4 is presented to remove the calibration and planarity procedure same as to reduce the conversion and setup cycle time. The augmented anvil block will not be removed from the indexer instead the sliding insert can be shifted to select the appropriate vacuum hole array. The sliding insert is composed of multiple vacuum hole that ranges from the different leadframe pitch design.

Fig. 4. Three-dimensional model of the improved anvil block design

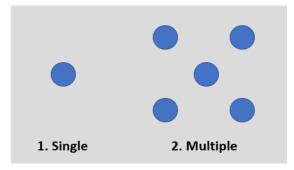

The vacuum hole is located underneath the leadframe pad wherein the diameter and the design of the hole can be modified depending on the size of the pad. Shown in Fig. 5 is the different design of vacuum hole: 1) for single vacuum hole design, the leadframe pad size ranges from 1 to 2.5 mm; and 2) multiple vacuum hole design is implemented to leadframe pad size greater than 2.5 mm. The advantage of compatible vacuum hole setting is to avoid the leadframe from moving when the glue is dispensed on top of the pad. Even glue dispense provides low tilting of the silicon die during die attach process.

Fig. 5. Vacuum hole design

The augmented design of anvil block as depicted in Fig. 6 is composed of two parts: 1) the base assembly, which connects the vacuum supply to the sliding inset; and 2) the sliding insert which is composed of multiple vacuum hole array.

Fig. 6. Augmented design of anvil block

When the vacuum is supplied to the fittings and vacuum groove, the rubber sealing ring eliminates the escape or leak between the base assembly and sliding insert. The seal ring also avoids loose contact between the sliding insert and base when sliding the insert or selecting the appropriate design of vacuum hole. Note that anvil block and vacuum holes vary with the product and design. Moreover, assembly process flow depends with the product and the technology [5-8].

| Ö       | • • • • • • • • • • • • • • • • • • • |         |                 | 3+8<br>3+8 |  |

|---------|---------------------------------------|---------|-----------------|------------|--|

| LABL1 U | UABEL2 UABEL3 UABEL4                  | LABEL 1 | LABEL 2 LABEL 3 | LABEL 4    |  |

Fig. 7. Selectable vacuum holes depending on package design requirement

The implementation of the improved design of anvil block tooling reduced the cycle time of conversion by 20%. The calibration and planarity check performed during setup is removed and instead calibration is performed quarterly or every preventive maintenance schedule. Through reduction of human intervention, assembly rejections encountered during setup are mitigated.

### 4. CONCLUSION AND RECOMMENDATIONS

The paper discussed a process solution and improvement with the augmented anvil block tooling that significantly improved the handling of leadframe or substrate strip during die attach process. The improved anvil block design helped reduce, if not eliminate, the assembly defect during die attach process such as crumpled strips, leadframe bending and dents, uneven bonding of die, localized insufficient epoxy, and misaligned die. Cycle time during setup is also improved.

Although the paper focused on the improvement in the anvil block tooling to address the die attach process related defects, continuous process and design improvement is important to sustain high quality performance of semiconductor products and its assembly manufacturing. Works and learnings discussed in [2, 9-10] are helpful in improving the assembly processes particularly the die attach process.

## COMPETING INTERESTS DISCLAIMER:

Authors have declared that no competing interests exist. The products used for this research are commonly and predominantly use products in our area of research and country. There is absolutely no conflict of interest between the authors and producers of the products because we do not intend to use these products as an avenue for any litigation but for the advancement of knowledge. Also, the research was not funded by the producing company rather it was funded by personal efforts of the authors.

## REFERENCES

1. Saha S. Emerging business trends in the semiconductor industry. Proceedings of PICMET '13: Technology Management in the IT-Driven Services (PICMET). USA. 2013;2744-2748.

- Xian TS, Nanthakumar P. Dicing die attach challenges at multi die stack packages. 35th IEEE/CPMT International Electronics Manufacturing Technology Conference. Malaysia: 2012;1-5.

- 3. Sumagpang Jr. A, Rada A. A systematic approach in optimizing critical processes of high density and high complexity new scalable device in MAT29 risk production using state-of-the-art platforms. Presented at the 22nd ASEMEP Technical Symposium, Philippines; June 2012.

- 4. Liu Y, Irving S, Luk T, Kinzer D. Trends of power electronic packaging and modeling. 10th Electronics Packaging Technology Conference. Singapore. 2008;1-11.

- 5. Harper C. Electronic packaging and interconnection handbook. 4th ed., McGraw-Hill Education, USA; October 2004.

- 6. May GS, Spanos CJ. Fundamentals of semiconductor manufacturing and process control. 1st ed., Wiley-IEEE Press, USA; May 2006.

- 7. Nenni D, McLellan P. Fabless: the transformation of the semiconductor industry. CreateSpace Independent Publishing Platform, USA; April 2014.

- 8. Doering R, Nishi Y. Handbook of semiconductor manufacturing technology. 2nd ed., CRC Press, USA; July 2007.

- 9. Rodriguez R, Graycochea Jr. E, Seguido R, Gomez FR. Die attach process optimization with enhanced epoxy control on leadframe package. Journal of Engineering Research and Reports. 2020;14(2);32-37.

- Abdullah Z, Vigneswaran L, Ang A, Yuan GZ. Die attach capability on ultra thin wafer thickness for power semiconductor. 35th IEEE/CPMT International Electronics Manufacturing Technology Conference. Malaysia: 2012;1-5.

NOFR